從芯片到系統 半導體封裝技術演進路線圖及其對計算機軟硬件技術開發的深刻影響

半導體封裝技術,作為連接芯片內部微觀世界與外部宏觀應用的橋梁,其演進歷程深刻塑造了計算技術的格局。從最初的保護性外殼到如今的高性能、高集成度系統級載體,封裝技術的每一次革新都成為驅動計算機軟硬件技術開發的關鍵力量。本文將勾勒半導體封裝技術的演進路線圖,并深入探討其對軟硬件開發的連鎖影響。

一、半導體封裝技術的演進路線圖

1. 傳統封裝時代(1970s-1990s):從通孔插裝到表面貼裝

- 雙列直插封裝(DIP):早期主流,通過引腳插入印刷電路板(PCB)的孔中實現連接。特點是結構簡單、成本低,但集成度低、占用面積大,限制了早期個人電腦和微處理器的性能與體積。

- 小外形封裝(SOP)、四方扁平封裝(QFP):隨著表面貼裝技術(SMT)興起,這些封裝形式將引腳分布在封裝體四周或底部,直接焊接在PCB表面。這顯著提高了PCB的組裝密度和可靠性,為更緊湊的硬件設計(如筆記本電腦、便攜設備)奠定了基礎。

2. 先進封裝崛起時代(1990s-2010s):追求高密度與高性能

- 球柵陣列封裝(BGA):用位于封裝底部的焊球陣列代替周邊引腳,極大地增加了I/O數量,縮短了信號路徑,提升了電氣性能和散熱能力。BGA成為CPU、GPU、芯片組等高性能芯片的標準封裝,直接推動了處理器頻率和功能的飛躍。

- 芯片級封裝(CSP):封裝尺寸接近芯片本身,實現了極致的微型化,廣泛應用于移動設備(如智能手機)中的存儲器、傳感器等,是移動計算硬件小型化的核心推手。

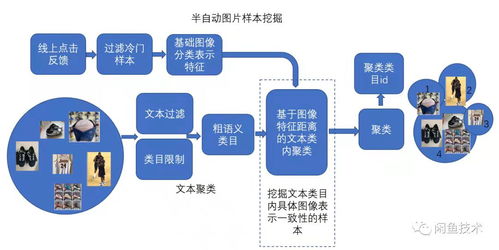

- 多芯片模塊(MCM)與系統級封裝(SiP):將多個不同功能的裸芯片(如邏輯、存儲、模擬)集成在一個封裝內。這實現了功能的異構集成,減少了互連延遲和系統體積,在通信設備、可穿戴設備中早期應用,預示了系統集成的未來方向。

3. 異構集成與“超越摩爾”時代(2010s-至今):走向系統級創新

- 扇出型封裝(Fan-Out):如臺積電的InFO技術,允許在芯片外部區域重新布線并放置I/O焊球,實現了更薄的封裝、更高的I/O密度和更好的散熱。這使手機應用處理器能集成更多功能并與內存更緊密耦合。

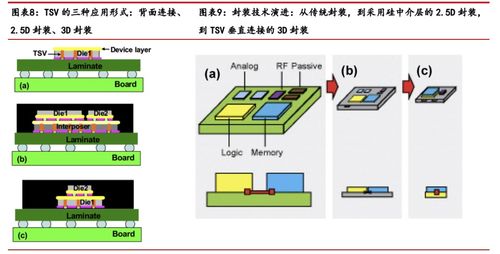

- 2.5D/3D封裝:

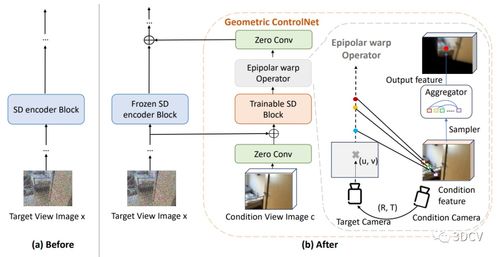

- 2.5D封裝:使用硅中介層(Interposer)將多個芯片并排連接在同一基板上,通過中介層中的高密度互連(如硅通孔TSV)實現芯片間的高速通信。典型代表是CoWoS(Chip on Wafer on Substrate),用于高端GPU、AI加速器,實現了海量數據的高帶寬傳輸。

- 3D封裝:將芯片在垂直方向上堆疊并通過TSV直接互連,極大縮短了互連長度,實現了前所未有的帶寬和能效。如HBM(高帶寬內存)與處理器的3D堆疊,解決了“內存墻”瓶頸,對高性能計算和人工智能至關重要。

- 芯粒(Chiplet)與先進互連:將大型SoC分解為多個較小、功能模塊化的芯粒,通過先進封裝(如Intel的EMIB、AMD的Infinity Fabric)進行異構集成。這降低了大規模芯片的制造成本和設計復雜度,并允許混合使用不同工藝節點的芯粒,成為延續摩爾定律經濟效益的關鍵路徑。

二、對計算機軟硬件技術開發的深刻影響

對硬件開發的影響:

- 性能突破:先進封裝通過縮短互連距離、增加帶寬,直接提升了處理器與內存之間的數據吞吐量,緩解了性能瓶頸。例如,3D堆疊的HBM使得AI訓練和科學計算的硬件效率成倍提升。

- 形態革新:封裝小型化使設備更輕薄(如超極本、折疊屏手機),而SiP和異構集成則催生了高度集成、功能豐富的硬件模塊(如系統模塊SoM),加速了物聯網終端、邊緣計算設備的創新。

- 設計范式轉變:芯粒架構催生了新的硬件設計模式。硬件開發者可以像“搭積木”一樣,選用不同供應商或工藝的預制芯粒,專注于系統架構和集成,從而加快產品上市時間,降低高端芯片的開發風險和成本。

- 散熱與功耗挑戰:高密度集成帶來了更高的功率密度,對散熱解決方案(如均熱板、液體冷卻)提出了極致要求,同時也推動了硬件層面的功耗精細管理技術發展。

對軟件開發的影響:

- 系統架構抽象層變化:對于采用3D堆疊、芯粒架構的硬件,操作系統和底層驅動需要能夠識別和管理這些在物理上緊密耦合但邏輯上可能獨立的計算單元、內存層次和互連拓撲。這可能需要新的硬件抽象層和資源管理模型。

- 并行與異構編程模型深化:為了充分發揮由先進封裝集成帶來的多核、眾核以及CPU、GPU、AI加速器、高速內存的協同計算能力,軟件并行編程模型(如OpenMP、CUDA)和異構計算框架(如SYCL、oneAPI)需要不斷演進,以更高效地調度和利用這些緊密集成的硬件資源。

- 內存與存儲層級優化:封裝內集成的超高速內存(如HBM)與較慢的系統主存、存儲構成了更復雜的內存層級。數據庫、大數據分析、科學計算等軟件需要優化數據放置和訪問策略,以匹配新的硬件內存特性,最大化性能收益。

- 安全與可靠性考量:復雜的異構集成系統可能引入新的安全邊界和故障點。軟件,特別是固件、虛擬化管理程序和安全模塊,需要適應這種新的物理形態,確保系統安全和可靠運行。

###

半導體封裝技術的演進,已經從單純的“保護與連接”,演變為決定系統性能、形態和成本的核心設計維度。其路線圖清晰地指向更高密度、更高帶寬、更異構集成的未來。對于計算機軟硬件開發者而言,理解并順應這一趨勢至關重要。硬件開發者需擁抱芯粒化和異構集成設計,軟件開發者則需為其打造的高效、復雜的計算系統編寫更智能、更能發揮硬件潛力的代碼。封裝與軟硬件的協同創新,正共同繪制著下一代計算系統的宏偉藍圖。

如若轉載,請注明出處:http://www.yanjuji.com.cn/product/77.html

更新時間:2026-02-24 12:24:50